本贴提供的工程是显示8行,每行显示10个数字,显示数字可由vio调试工具修改,先上效果图,具体工程文件见留言区1楼。

如果网友想移植修改显示行数和每行字符个数,下面列出需要修改的地方,详细的设计思路可参考AXC720开发板配套的教程资料。有任何问题可以留言或小梅哥技术交流群咨询。

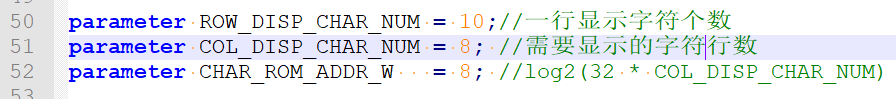

1、顶层文件dync_char_tft.v中的关于显示字符个数的参数

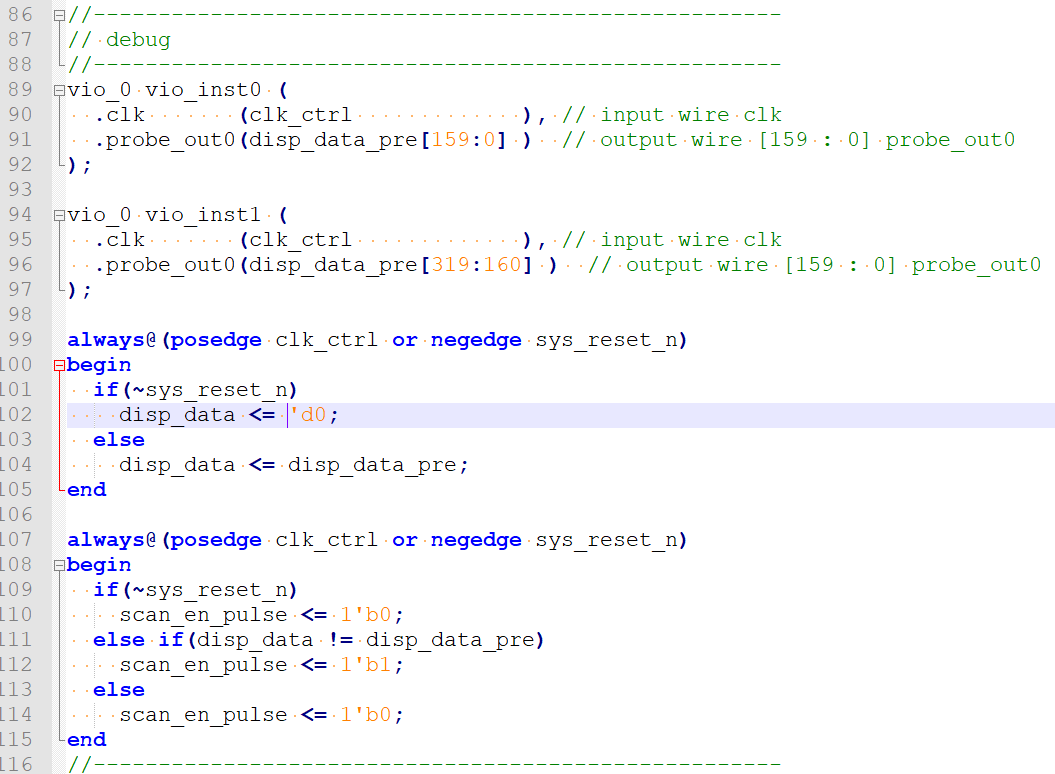

2、本工程显示字符的来源是利用VIO调试工具产生,显示的字符总数变化后,这里也需要做相应的修改,比如这里一行显示10个数字,显示8行,那总共就是8*10个数字,每个数字需4bit,则共需320bit,由于一个VIO的一个端口最大位宽256bit,为了实现320bit数据,这里例化了2个,每个位宽160,拼接正好320bit,这里需要用户根据实际情况来修改,当然如果不采用VIO产生数字,内部逻辑产生数据也是可以的,位宽计算方法类似。显示数字的更新是在数据有变化的情况下才去启动一次扫描,屏幕显示就更新。

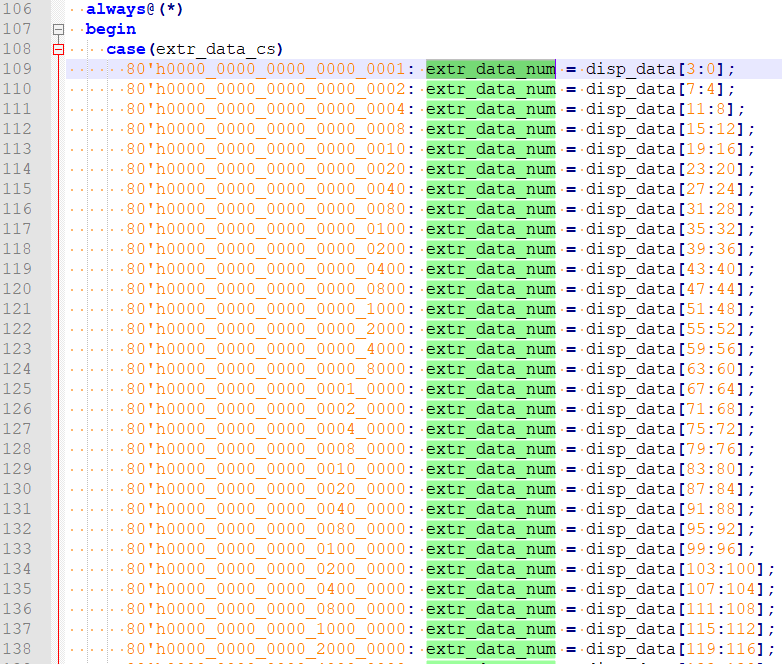

3、data_scan_ctrl.v文件需要修改如下代码,这个always块的代码需要根据实际情况修改,这里总共显示是80个字符,extr_data_cs就是80bit的片选信号,每个bit对应一个待显示数据的更新,哪个bit为1,对应的要显示的数据就更新赋值给extr_data_num。这个由于显示的数字比较多,case的分支就比较多,这里暂时还没有想到比较简单的写法,目前代码可以满足80个以下字符的显示,如果超过80个字符,这里case的分支需增加。

|  |小黑屋|Archiver|芯路恒电子技术论坛

|鄂ICP备2021003648号

|小黑屋|Archiver|芯路恒电子技术论坛

|鄂ICP备2021003648号