有网友在使用Vivado对DDR3相关例程进行仿真时出现init_calib_complete一直未变成高电平,正常情况下,init_calib_complete一般在110us左右就会变为高电平,如果在仿真跑到200us后init_calib_complete仍未变成高电平,这种情况下可以将仿真停下来了不用继续仿真了。这个时候提供两种解决思路

思路一:重新生成输出

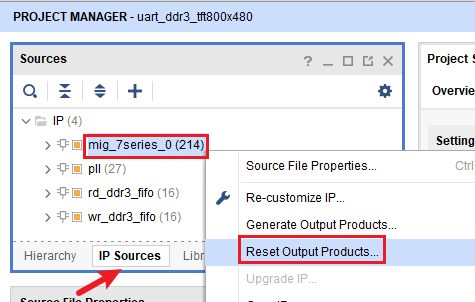

1、在IP栏找到MIG IP ,鼠标右键在选项中找到Reset Output Products...并进行点击,这个时候就将IP进行了“复位”处理,IP相关的文件进行了一次清理。

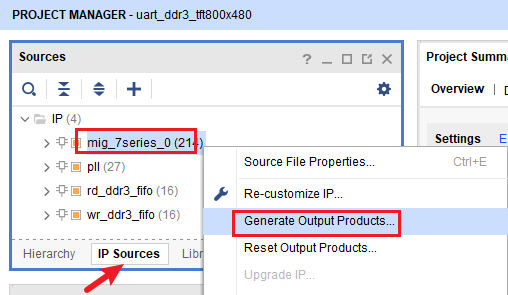

2、在IP栏找到MIG IP ,鼠标右键在选项中找到Generate Output Products...并进行点击,这个时候就将IP进行了重新生成操作。

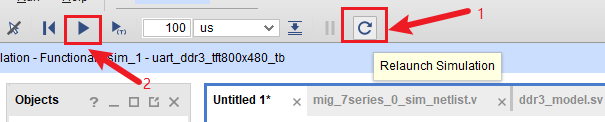

3、回到仿真界面,先点击下图1处图标(Relaunch Simulation),然后点击2处图标(Run All),重新进行仿真。对于修改了原代码或IP文件,都可以通过这两个步骤进行仿真的更新或重启。

4、一般经过上面3个步骤可以解决问题,如果是自己编写的仿真文件,经过上述步骤仍未解决,可以检查MIG IP时钟复位是否正常,仍未解决或有其他新的问题可以下方留言或小梅哥FPGA技术群咨询。

思路二:检查信号位宽

如果用户对mig核配置进行过修改,例如修改过DDR型号、数据位宽等参数,却没有及时修改仿真顶层中相关信号位宽,也有可能出现该情况。此时用户需要核对仿真顶层中ddr3_model和mig信号位宽是否正确。 |  |小黑屋|Archiver|芯路恒电子技术论坛

|鄂ICP备2021003648号

|小黑屋|Archiver|芯路恒电子技术论坛

|鄂ICP备2021003648号