在前面fpga_led小节讲解了智多晶fpga的基本开发流程,并讲解了使用Modelsim编译SA5Z系列器件库。本节我们在fpga_led工程的基础上讲解智多晶fpga联合Modelsim进行仿真验证的流程。

1.1 编写Verilog仿真设计代码。

仿真文件的编写流程与设计文件的编写流程一致。点击“设计管理”选项以打开设计文件管理工具。注意,如果已经打开了其他工具(调试,下载,物理约束,时序约束等其他窗口,必须先关闭那些窗口,才能打开设计管理)。

在打开的设计管理器中,依次点击“文件”->“新建文件”以新建一个文件,或者使用Ctrl + N快捷键。

在打开的文件中输入代码内容, LED流水灯实验的仿真文件,可以使用下述代码。

`timescale 1ns/1ns

module fpga_led_tb();

xsGSR xsGSR_INST(.GSR(1'b1));

xsPWR xsPWR_INST(.PUR(1'b1));

reg Clk;

reg Rst_n;

wire [3:0]Led;

fpga_led fpga_led(

.Clk(Clk),

.Rst_n(Rst_n),

.Led(Led)

);

initial Clk = 1;

always#20 Clk = ~Clk;

initial begin

Rst_n = 0;

#201;

Rst_n = 1;

#200;

#4000_000_000;

$stop;

end

endmodule

注:由于使用了 XIST IP 核的子模块中使用了全局 XsGSR_INST 变量和一个XsPWR_INST 变量。由于仿真不具有这个全局变量,所以需要在顶层文件的模块中添加这两个变量如下:

xsGSR xsGSR_INST(.GSR(1'b1));

xsPWR xsPWR_INST(.PUR(1'b1));

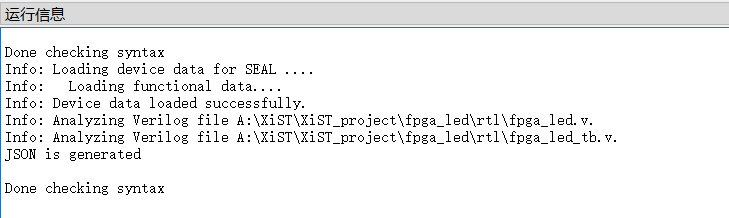

设计完成后进行语法检查并保存

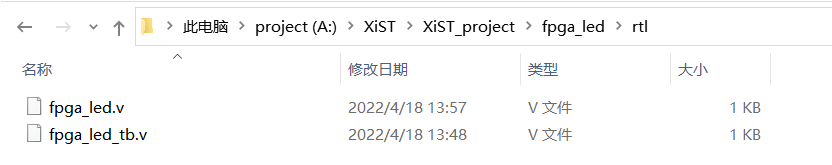

语法检查无报错后保存到工程的rtl文件夹下。

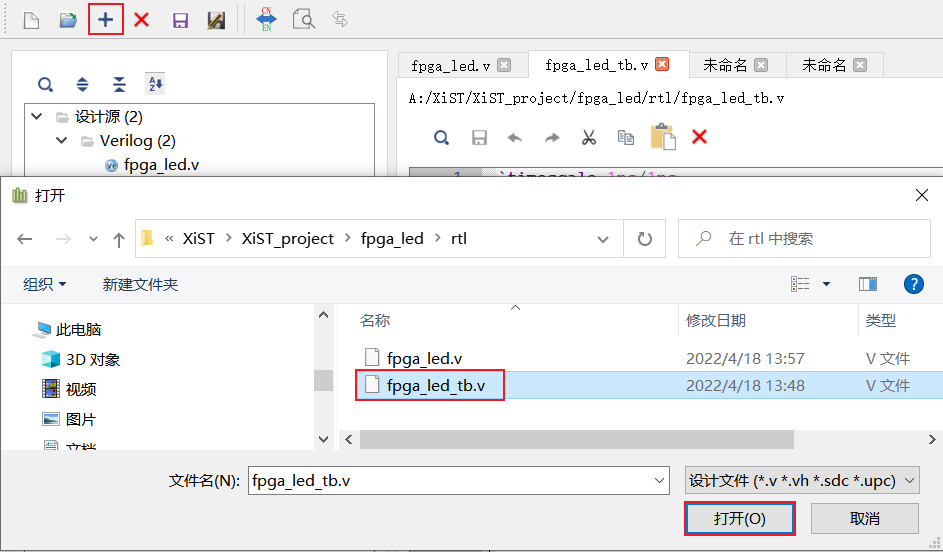

点击“+”—>选择“fpga_led_tb.v”添加设计文件到工程。

]

仿真文件设计完成后我们就可以利用Modelsim进行工程的功能仿真测试。

1.2 建立 Modelsim 工程并添加仿真文件

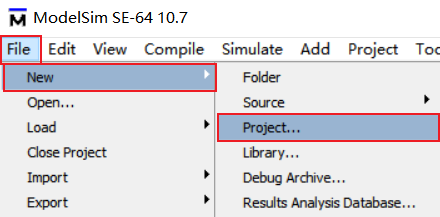

打开Modelsim,在 Modelsim 中建立一个新的 project,选择File->New->project,如下图所示:

进入建立新工程的设置界面。

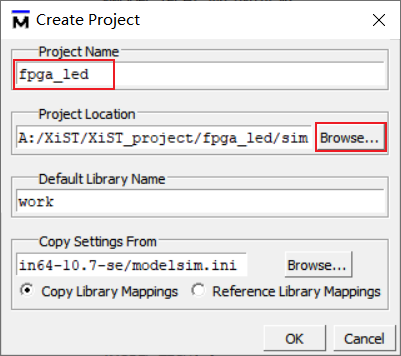

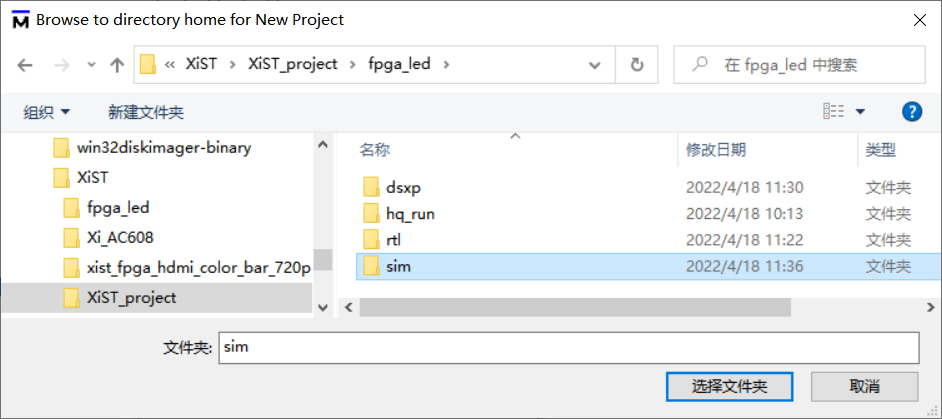

在“Project Name”栏中填写工程名,这里我们把工程命名为相对应的工程名“fpga_led”,“Project Location”是工程路径,点击“Browse”进行设置,根据需要我们把仿真工程保存到我们设计工程下,新建一个sim文件夹并选择。

然后点击【OK】 按钮,进入下图所示界面:

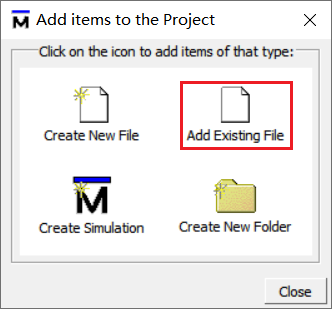

从该图的选择窗口中看出,有四种操作可选择:Create New File(创建新文件)、Add Existing File(添加已有文件)、Create Simulation(创建仿真) 和 Create New Folder(创建新文件夹)。

这里选择“Add Existing File”(添加已有文件)。

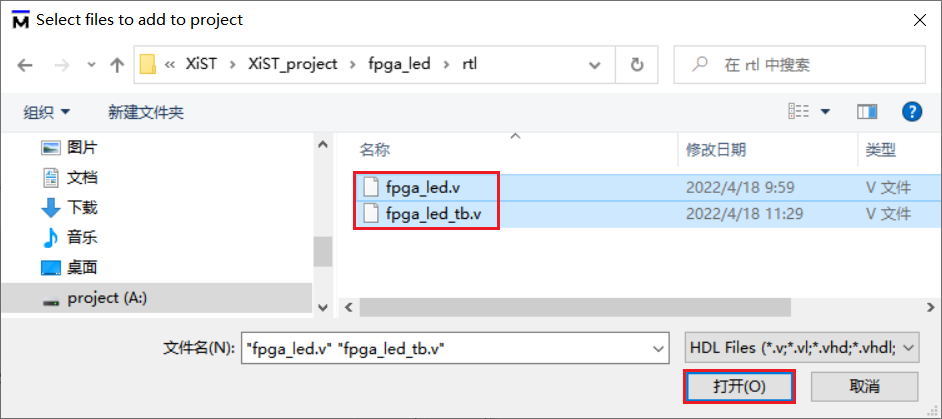

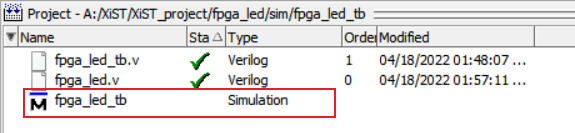

添加我们的工程设计文件“fpga_led.v”、 “fpga_led_tb.v”,如下图所示:

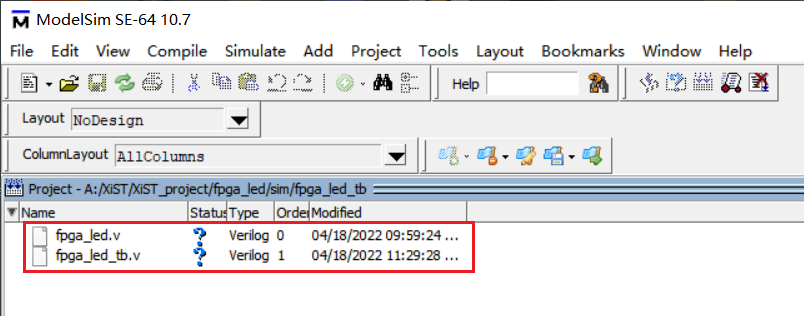

现在可以看到在Modelsim中添加了我们的工程设计文件,

1.3 编译仿真文件

编译的方式有两种:

1、Compile Selected(编译所选文件)。编译所选功能需要先选中一个或几个文件,执行该命令可以完成对选中文件的编译;

2、 Compile All(编译全部文件)。编译全部功能不需要选中文件,该命令是按编译顺序对工程中的所有文件进行编译。

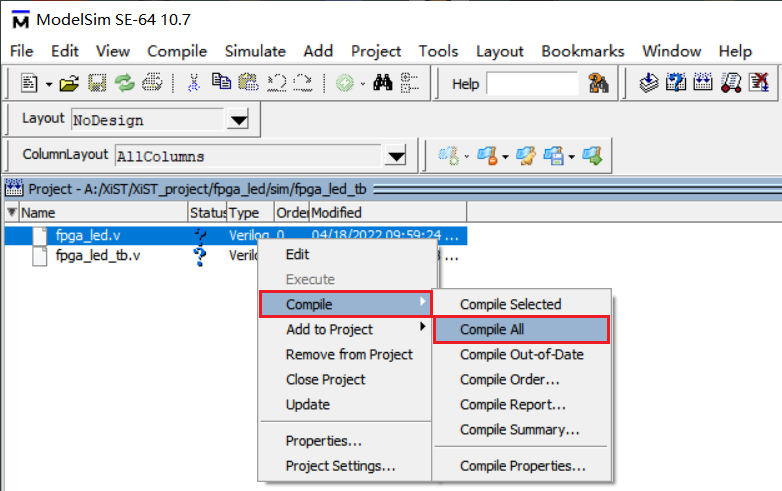

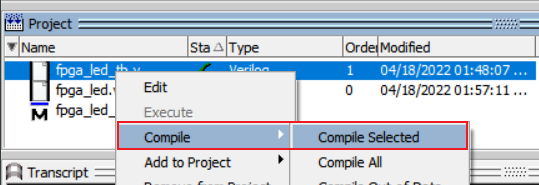

右击需要编译文件,选择 Compile->Compile All 如下图

所示:

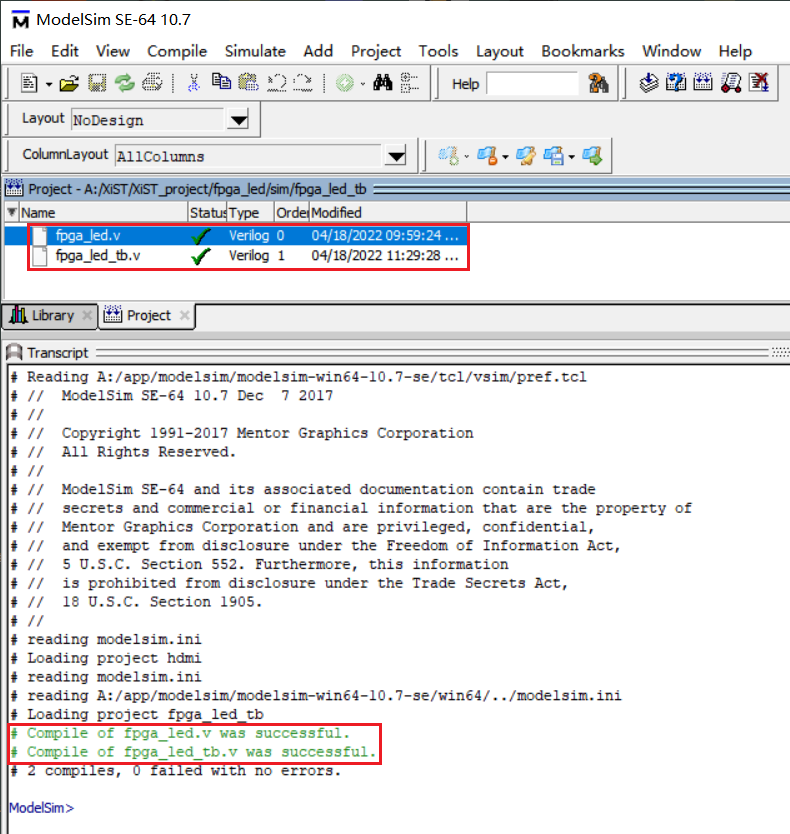

文件编译后“Status”中的“?”变为“√”表示编译通过。

还有两个在设计中不希望出现的状态:编译错误(显示红色的“×”)和包含警告的编译通过(对号的后面会出现一个黄色的三角符号)。

编译错误即 Modelsim 无法完成文件的编译工作。通常这种情况是因为被编译文件中包含明显的语法错误,Modelsim 会识别出这些语法错误并提示使用者,使用者可根据 Modelsim 的提示信息进行修改。

1.4 配置仿真环境

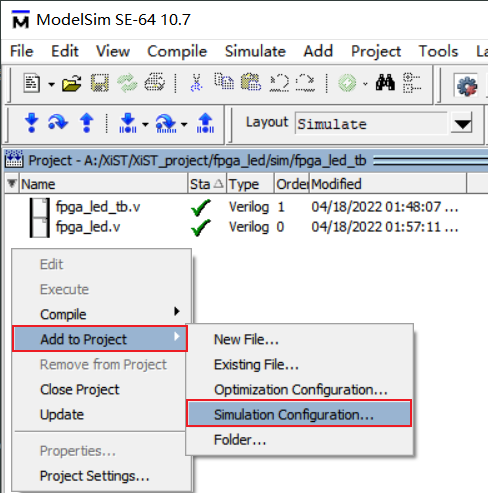

编译完成后,接下来我们就开始配置仿真环境,我们在project 状态栏中右键点击,选择“Add to Project”-> “Simulation Configuration…”并点击。

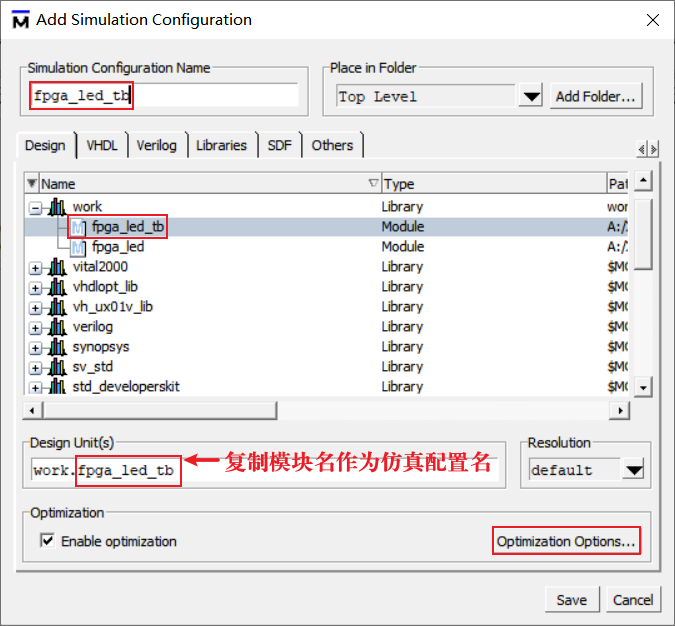

进入Add SimulationConfiguration 页面,我们在 Design 标签页面中选择 work 库中的“fpga_led_tb”模块作为设计顶层,点击复制模块名作为仿真配置“Simulation Configuration Name”的命名,确保命名保持一致。在复杂的工程设计中,我们可以设计多个不同的仿真配置顶层对工程进行仿真测试。

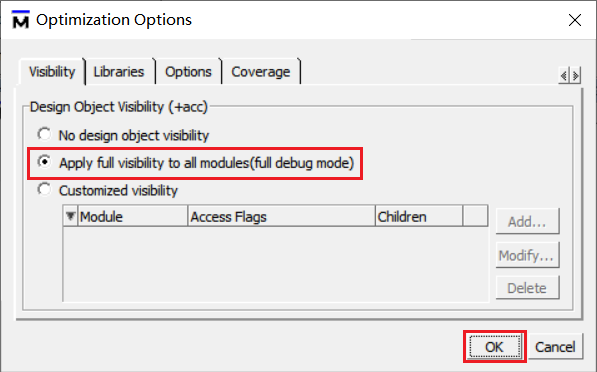

点击“Optimization Options...”,在“Optimization Options..”设置栏选择“Apply full visibility to all modules(full debug mode)”,点击“OK”。

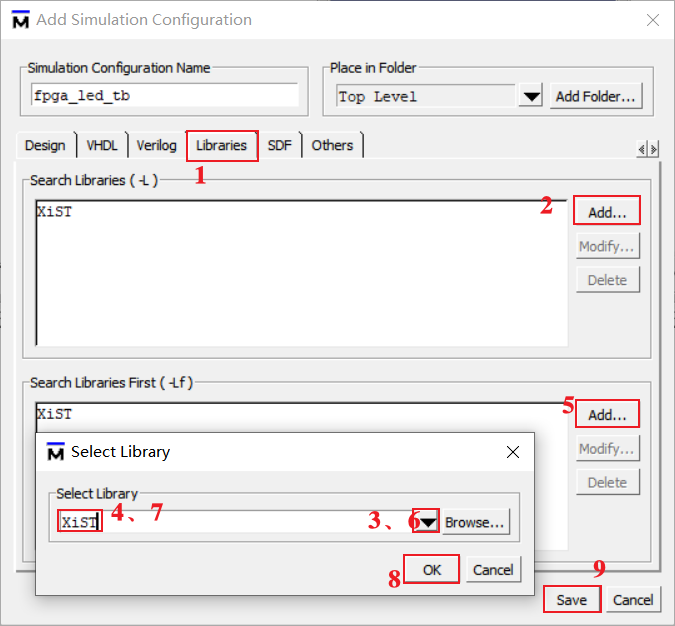

点击进入“Libraries” 设置栏,在“Search Libraries (-L)”一栏点击“Add…”添加我们新建的智多晶的库文件“XiST”,在“Search Libraries First (-Lf)”同样选择库文件“XiST”,点击“Save”。

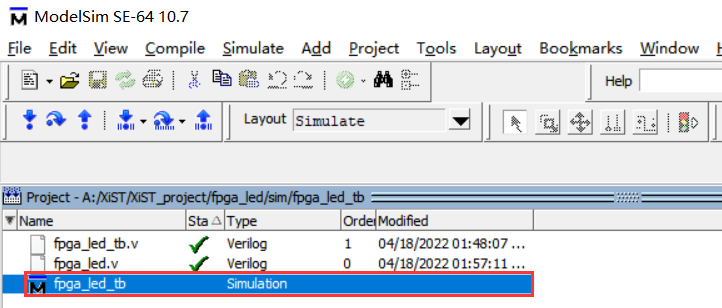

保存配置后在“project”栏产生了仿真配置文件“fpga_led_tb”。

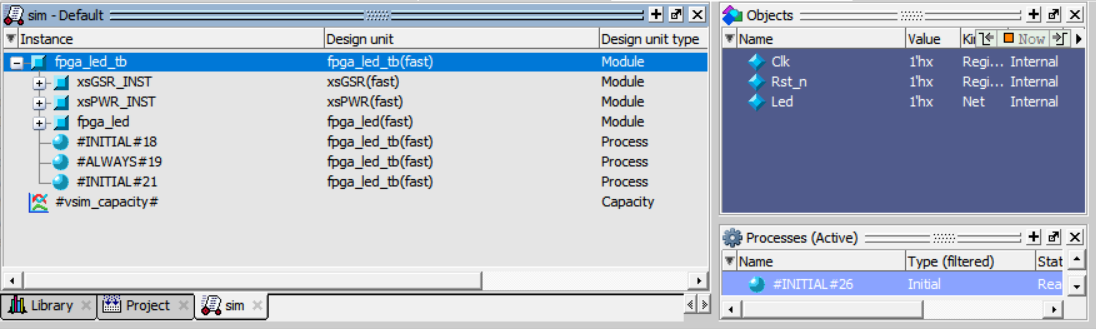

点击“fpga_led_tb”文件,进入“sim”仿真界面。

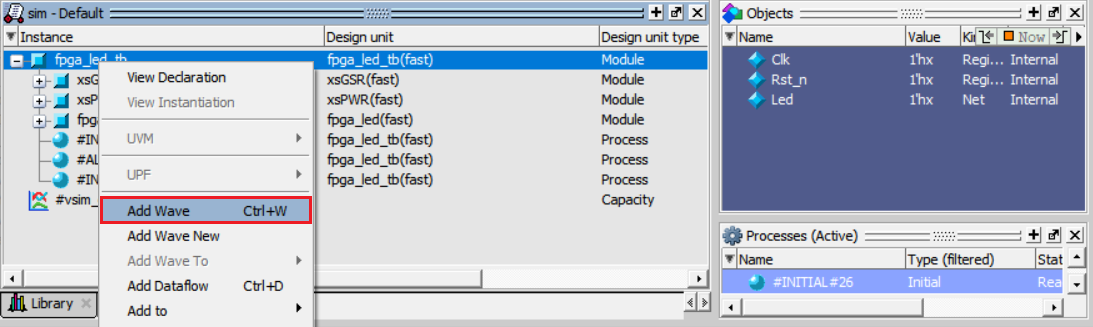

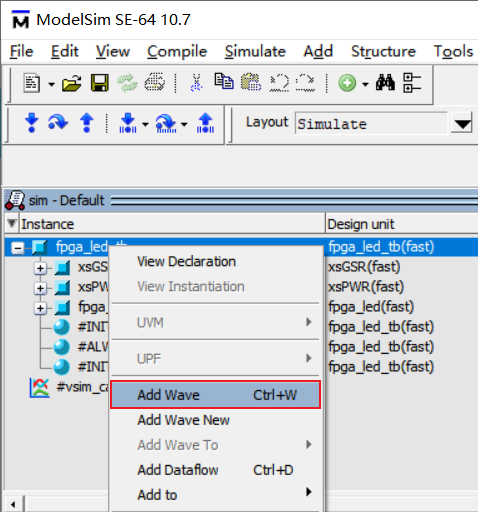

在“sim”界面我们可以添加我们想要观察模块的波形,选中模块,右键点击选择“Add Wave”。

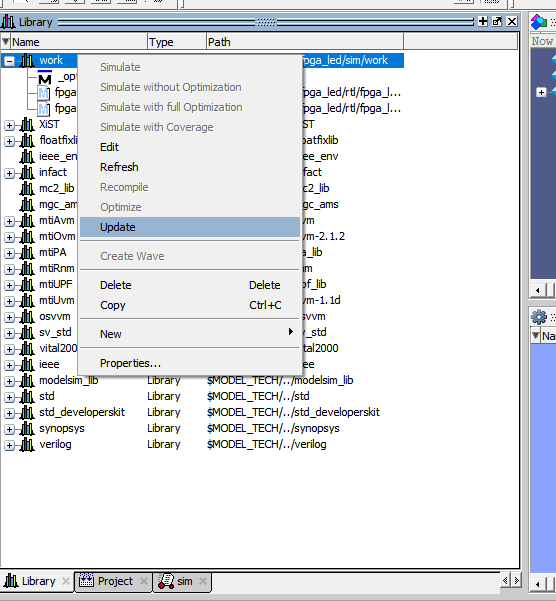

添加好波形后回到“Librariy”栏

右键单击“work”点击Update将“fpga_led_tb”文件更新在“work”栏

若操作界面底部仍显示

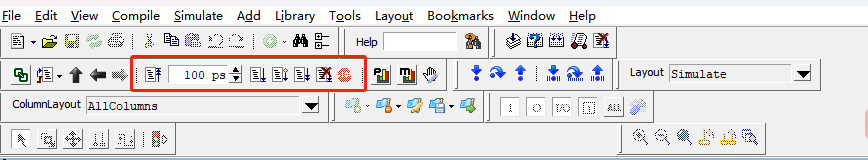

在该行依次点击

“Stop” 、Resart

、Resart  、全选

、全选 、”Run all“

、”Run all“

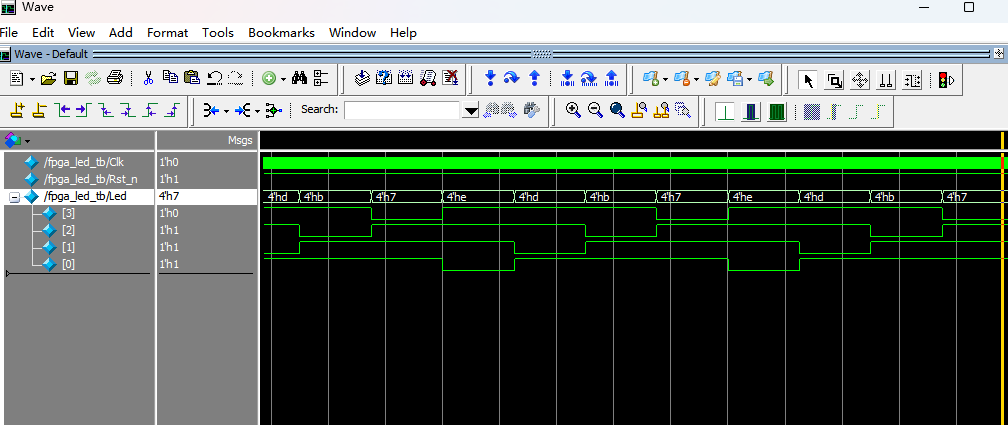

“Run all”之后可以回到“Wave”观察模块的仿真。

此时点击“Zoom Full”可以快速观察到波形。

在波形图中可以观察到,通过延时计数,实现了对4个led的亮灭控制。

在开发过程中,在更改设计文件后,点击保存并检查语法无误后重新运行程序。在Modelsim中,我们进入“Library”界面,在“Work”目录下对“fpga_led_tb”、“fpga_led”进行重新“Recompile”,重新进行仿真波形的加载。

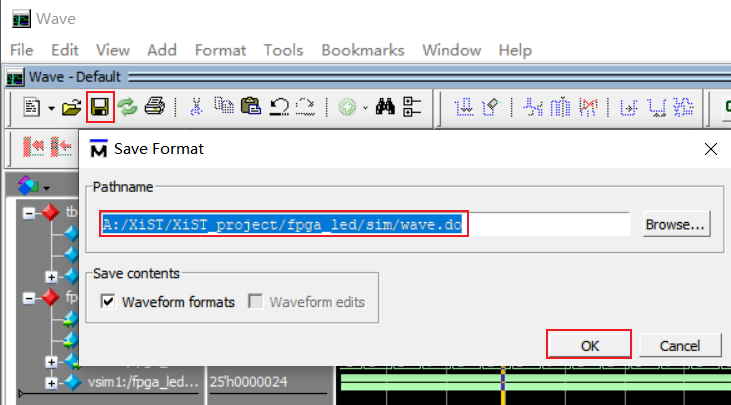

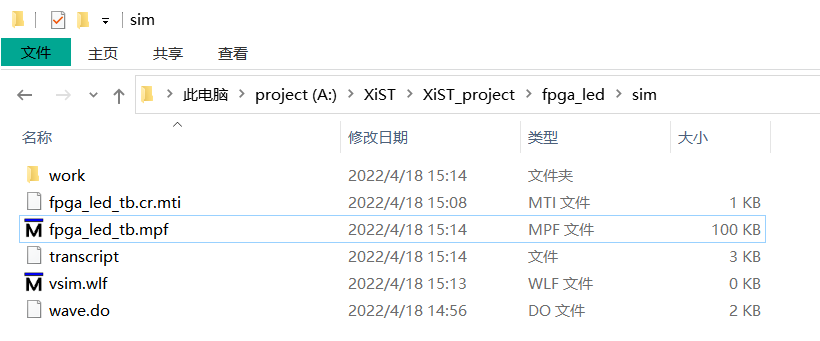

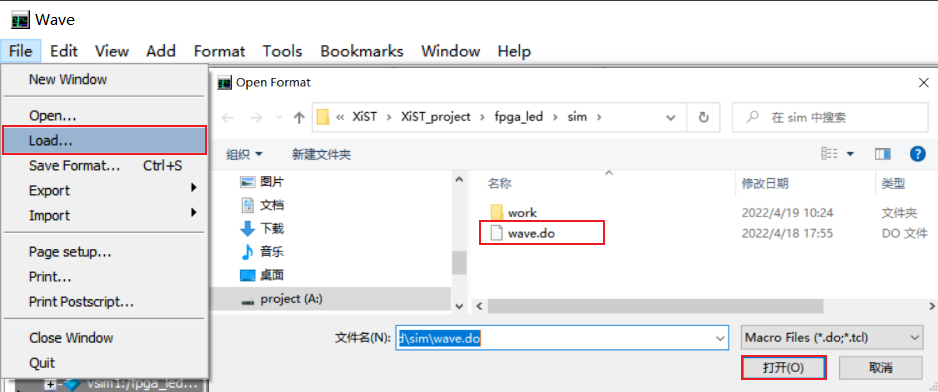

点击保存可以把我们添加的模块信号进行保存,方便下次快速调用。点击保存图标后,添加的信号文件“wave.do”会默认保存在工程的仿真文件sim中。

在关闭仿真后,读者需要重新打开仿真,只需要打开“.mpf”文件。

在首次打开“.mpf”时,系统不会默认选择用Modelsim打开,读者就需要手动设置“.mpf”文件打开的方式,安装多个版本Modelsim的读者还需要注意设置对应版本的Modelsim软件,实验安装的版本为modelsim-win64-10.7-se。

如果是使用我们提供的源码工程,工程在经过清理后在首次进入Modelsim时需要分别对“.v”文件进行编译,这里进行全编译编译会报错无法全部通过。

运行仿真配置文件“fpga_led_tb”。

重新添加波形。

如果读者保存过波形文件“wave.do”,可以快速调用“wave.do”进行波形的添加,在进行复杂项目的开发时调用“wave.do”会节省我们仿真的时间。

对于进行智多晶fpga开发运用Modelsim仿真的流程就介绍到这,读者可自己建立工程熟悉流程,在实验过程中有所疑问的欢迎大家到我们的技术群或芯路恒官方论坛(http://www.corecourse.cn)留言提问。

更多智多晶FPGA相关资料,请查看下述汇总贴

【智多晶FPGA-001】小梅哥智多晶FPGA产品使用自助服务手册:

http://www.corecourse.cn/forum.php?mod=viewthread&tid=28724

案例源码

|小黑屋|Archiver|芯路恒电子技术论坛

|鄂ICP备2021003648号

|小黑屋|Archiver|芯路恒电子技术论坛

|鄂ICP备2021003648号